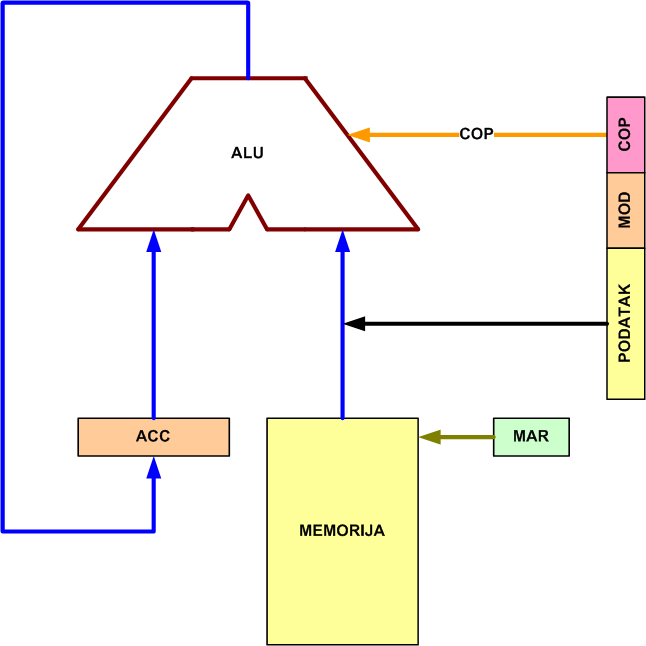

Arhitektura FTN_EDU_Pro procesora

Arhitektura procesoar FTN_EDU_Pro je specificirana sa idejom da se demonstrira pristup projektovanju računarskog hardvera. Takođe, obuhvaćeni su aspekti simulacije i modeliranjem datog hardvera u nekom od HDL (Hardware Description Language) jezika. Opis elemenata arhitekture FTN_EDU dat je u tekstu Arhitektura procesora FTN_EDU.

Dužina instrukcije ovog procesora je 16 bita. Značenje pojedinih polja u formatu instrukcije je:

- ADRESA (Bitovi 0 – 7) – adresa

- MOD (Bitovi (8 – 11) – način adresiranja

- COP (Bitovi 12 – 15) – operacija koja se izvršava

U prvoj verziji arhitekture, shodno formatu instrukcije, karakteristike procesora su sledeće:

- Dužina registarskog i memorijskog operanda – 16 bita

- Dužina neposrednog operanda – 8 bita

- Dužina adresne reči – 8 bita

- Dužina procesorske reči – 16 bita

- Broj instrukcija – 16

Procesor obezbeđuje dva načina adresiranja:

- Direktno adresiranje

- Neposredno adresiranje

Procesor poseduje i stek obima 16 lokacija, koji funkcioniše po principu da SP (Stack Pointer) ukazuje na prvu slobodnu lokaciju. Dužina reči koja se pati u steku je 8 bita.

Skup operacija

Skup operacija procesora čine:

- Sabiranje

- Oduzimanje

- Množenje

- Deljenje

- Poređenje

- Logičko I

- Logičko ILI

- Invertovanje

- Pomeranje

- Push

- Pop

- Jump

- Load

- Store

- Halt

Detaljan prikaz arhitekture procesora, uključujući i specifikaciju simboličkog mašinskog jezika obrađeni su u master radu studenta Marijane Gudović. Tekst ovog master rada je sdržan u datoteci Specifikacija arhitekture FTN_RISC [PDF].