Temeljeći rezultate razvoja RISC-V arhitekture firama SiFive je postala prva kompanija koja je realizovala integrisano kolo na bazi RISC-V ISA arhitekture. Proizvodi SiFive uključuju SoC i razvojne ploče. Kompaniju su osnovali istraživači sa Univerziteta Berkli, na kome je i razvije RISC-V ISA arhitektura. Krajem novembra 2016. godine SiFive je realizovala integrisano kola SoC tipa, Freedom Everywhere 310 i HiFive razvojnu ploču. U oktobru 2017. godine je predstavio kolo U54-MC, kojje predstavljalo prvi RISC-V, 64 – bitni procesor sa četiri jezgra. Ovaj procesor je potpuno podržavao operativni sistem na Linux bazi. Februara 2018. godine SiFive je predstavio HiFive Unleashed razvojnu ploču sa 64 – bitnim SoC kolom sa četiri U54 jezgra. Aprila 2018. godine kompanija je dobila značajna sredstva za razvoj serije C između ostalog i od Intel Capital.

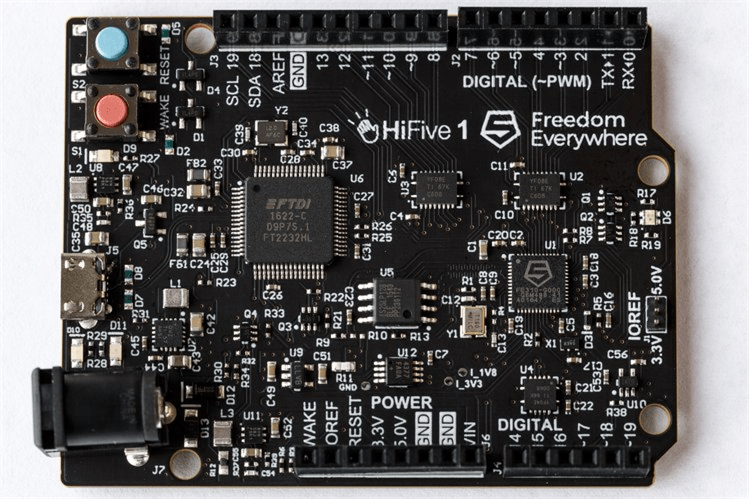

HiFive1 i HiFive1 Rev B razvojne ploče

HiFive1 je jeftina razvojna ploča, kompatibilna sa Arduinom namenjena za izradu prototipa i razvoj RISC-V aplikacija. Karakteristike uređaja su:

| Mikrokontroler | FE310-G000 |

| Radni napon | 3.3V i 1.8V |

| Ulazni napon | 5 USB ili 7 – 12VDC jack |

| I/O naponi | Podržani su i 3.3V i 5V |

| Digitalni I/O kontakti | 19 |

| PWM kontakti | 9 |

| SPI kontroleri/HW CS kontakti | 1/3 |

| Spoljašnji interrupt kontakti | 19 |

| Spoljašnji Wakeup kontakti | 1 |

| Flash memorija | 128Mbit off – Chip (ISSI SPI Flash) |

| Host interface (microUSB) | Program, Debug i Serial Communications |

| Težina | 22g |

HiFive1 razvojna ploča može da se programira korišćenjem Freedom E SDK i Arduino IDE softverskih paketa. Osnovno uputstvo za rad sa SiFive HiFive1 može se preuzeti sa adrese – SiFive HiFive1 Getting Started Guide.

U međuvremeni SiFive je projektantima ponudio novu verziju HiFive1 razvojne ploče sa oznakom HiFive1 Rev B. Na ovoj ploči se nalazi nova verzija procesora FE310 – G002, a ima i mogućnost bežične komunikacije putem ugrađenih komunikacionih modula Wi-Fi/Bluetooth. Uloga bežičnog modema obezbeđena je preko ESP32 koprocesora. Novinu kod FE310 kola predstavlja ugrađena I2C periferija, kao i dodatna UART komunikacija (ukupno dve), što omogućava priključenje svih vrsta senzora, aktuatora i ostalih uređaja. Takođe, USB debug interfejs je unapređen u Segger J-Link. Informacije o razvojnim pločama HiFive1 i HiFive1 Rev B mogu se naći na WEB stranici SiFive/Board.

Ako se uporede FE310-G000 i FE310-G002 mogu se uočiti sledeće razlike:

| FE310-G000 | FE310-G002 | |

| CPU | SiFive E31 | SiFive E31 |

| RISC-V Debug Spec | Version 0.11 | Version 0.13 |

| Low-power Sleep Mode | No | Yes |

| Always-on Domaun | 1.8V | 3.3V |

| Hardware I2C | None | 1 |

| UART | 1 | 2 |

| QSPI/SPI | 1/1 with 3 Chip Select | 1/1 with 3 Chip Select |

| PWM | 9 | 9 |

| GPIO | 19 | 19 |

Razlike između HiFive1 i HiFive1 Rev B razvojnih ploča su:

| HIFIVE1 | HIVIFE1 Rev. B | |

| Procesor | SiFive FE310-G000 | SiFive FE310-G002 |

| USB Debug | FTDI FT2232 | Segger J-Link |

| Wireless Network | None | WiFi & Bluetooth |

| Low-power Domain | No | Yes |

| I/O Voltage | 3.3V Level-shifted 5.0V | 3.3V |

| Code Storage | 16MB QSPI NOR Flash | 4MB QSPI NOR Flash |

| Form Factor | 68x51mm | 68x51mm |

Programiranje razvojnog modula HiFive1

Postoje tri načina programiranja HiFive1:

- Korišćenjem Freedom E SDK razvojnog okruženja. Freedom E SDK je repozitorijum sa demo programima, benchmark programima i programskim paketima za podršku ravojnim modulima (Board Support Packages, BSP);

- Korišćenjem Freedom Studio razvojnog okruženja. Freedom Studio je najbrži način da se počne sa programiranjem SiFive hardvera. Freedom Studio je realizovan na bazi popularnog Eclipse IDE razvojnog okruženja i povezan je sa odgovarajućom mrežom alata i praktičnim primerima iz Freedom E SDK. Kompatibilan je sa svim SiFive RISC-V razvojnim modulima;

- Korišćenjem Arduino IDE razvojnog okruženja.

Literatura

- Waterman, A., „Design of the RISC-V Instruction Set Architecture„, PhD Dissertation in Computer Science, University of California, Berkeley, 2016

- Waterman, A., „Design of the RISC-V Instruction Set Architecture“, EE and CS University of California at Berkeley, Technical report No. UCB/EECS-2016-1, January 3, 2016

- Clark, M., Hoult B., „rv8: A High Performance RISC-V to x86 Binary Translator„, First Workshop on Computer Architecture Research with RISC-V (CARRV 2017), Boston, MA, USA, October 2017

- Menon, A. et al, „Shakti-T: A RISC-V Processor with Light Weight Security Extensions„, Conference on Hardware and Architectural Support for Security and Privacy (HASP), Toronto, ON, Canada, June 25, 2017

- Patterson, D. A., Hennessy, J. L., „Computer Organization and Design RISC-V Edition: The Hardware Software Interface„, 1st Edition, Morgan Kaufmann, 2017

- Waterman, A., Asanović, K., ed., „The RISC-V Instruction Set Manual: Volume I – User level ISA“, Document Version 2.2, SiFive & University California at Berkeley Technical report

- Scotti, G., Yoni, D., „A Fresh View on the Microarchitectural Design of FPGA – Based RISC CPUs in the IoT Era“, Journal of Low Power Electronics and Applications, February 2019